# intel

# **CK100 Clock Buffer Preliminary EMI Layout Guideline**

Rev. 0.51 February 1998

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications. Intel may make changes to specifications and product descriptions at any time, without notice.

Patent Royalty Payments if applicable are not the responsibility of Intel.

Third-party brands and names are the property of their respective owners.

Copyright ©1998, Intel Corporation, All Rights Reserved.

### CK100 Clock Buffer Preliminary EMI Layout Guideline (Rev 0.51)

#### Scope:

This document describes an example of a layout for reducing emissions from a CK100 SDRAM Clock Buffer motherboard design.

#### **Background:**

The CK100 Buffer Part (CKBUF) takes an output clock from the Chipset and makes 18 copies for the provision of clock signals to SDRAM DIMMs. These output clocks are synchronized by definition.

Unless the outlined design guidelines are followed there is a high risk of excessive EMI problems at the higher clock harmonics.

#### Specifics:

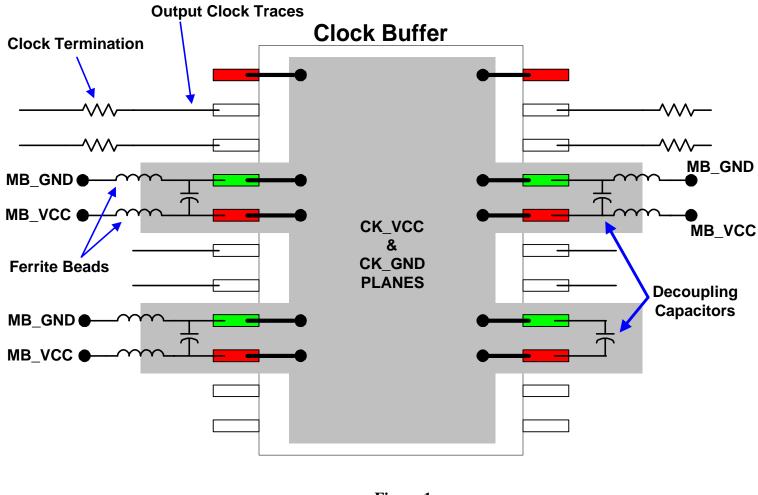

Figure 1 (overleaf) illustrates one example of a PCB layout that has been shown to reduce system EMI levels related to the CK100 Buffer Part and its associated SDRAM Clock Output traces.

The critical aspects are:

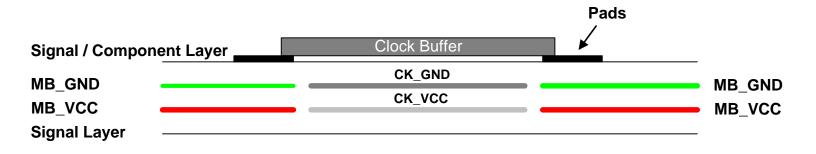

Dedicated Power and Ground Planes for Clock Buffer (CK\_VCC and CK\_GND).

These planes should be 'cut out' planes on the normal VCC and GND layers of the PCB (Figure 2).

CK\_VCC and CK\_GND are connected to MB\_GND and MB\_VCC through low value ferrite beads (5 Ohms @ 100MHz). These beads should span the void area created by the plane split.

The motherboard layout should include provision for about 14 beads (7 on VCC, 7 on GND. This includes beads for the IIC VCC and IIC GND). The minimum number of beads should be populated while still maintaining the required rise time at the DIMMs (1V/nS).

Decoupling Capacitors between CK\_VCC and CK\_GND (in the order of 6 1000pF) should be placed over the CK\_VCC and CK\_GND "wings".

The Output Clock traces to the DIMMs should not, under any circumstances cross over any of the void areas created by the CK\_VCC and CK\_GND planes. These traces must have a complete plane (VCC or GND) under their entire routing length.

## CK100 Clock Buffer Preliminary EMI Layout Guideline (Rev 0.51)